The last time we checked in with [Downtown Doug Brown], he had some cheap Altera USB Blaster clones that didn’t want to work under Linux. The trick at that time was to change the device’s 24 MHz clock to 12 MHz. This month, he’s found some different ones that don’t work, but now the clock change doesn’t work. What’s the problem?

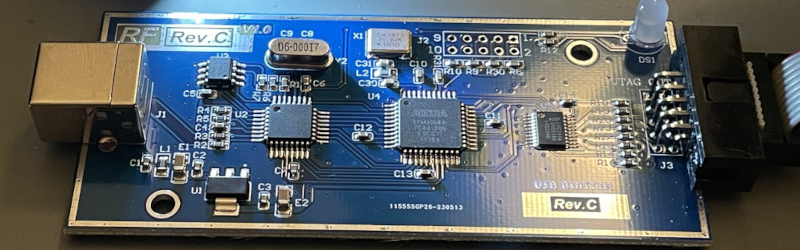

He also picked up a Terasic clone, which does work on Linux and is considered, according to [Doug], the best of the clones. The units were superficially similar. So what follows is a lot of USB tracing and dumping of the CPLD chip’s configuration.

The problem is that even though CPLDs are relatively simple, relative is a — well — relative word. It is still a lot of work to reverse engineer a CPLD bitstream. However, he did find some public VHDL source code that acted the same so he presumed it shared a common problem with the original configuration.

Inspecting the code, he realized that there was no delay between a critical part of the protocol. For some reason, Windows didn’t seem to care, but it was enough to upset the Linux driver. At least, that was the theory.

Theory, in this case, translated to practice. As a bonus, the new code even made the original units work at full speed. Although it isn’t technically accurate, you can think of CPLDs as little FPGAs, and sometimes, they are more approachable for beginners. They are also great when you don’t need a full-blown FPGA.